|

||||||||

You may redistribute this newsletter for non-commercial purposes. For commercial use contact jack@ganssle.com. To subscribe or unsubscribe go here or drop Jack an email. |

||||||||

| Contents | ||||||||

| Editor's Notes | ||||||||

|

Tip for sending me email: My email filters are super aggressive. If you include the phrase "embedded muse" in the subject line your email will wend its weighty way to me. |

||||||||

| Quotes and Thoughts | ||||||||

Any problem in computer science can be solved with another layer of indirection, except of course for the problem of too many indirections. Bjarne Stroustrup |

||||||||

| Tools and Tips | ||||||||

|

Please submit clever ideas or thoughts about tools, techniques and resources you love or hate. Here are the tool reviews submitted in the past. In response to the buck50 logic analyzer in the last Muse, Stephen Green sent in a link to a £6.80 version. Also in reference to the buck50 LA, Paul Brower warned there are a lot of fake Blue Pill boards around. As he wrote: "Wouldn't want to see a reader frustrated and beating their head against an O-scope trying to figure out why it isn't working as expected. " More info here and here. Gary Maxwell sent this (college professors please note well!):

That is a great thought. Test equipment has historically been too expensive for education and hobbyists. Sure, there are some nice inexpensive USB scopes around, but the buck50 technology could literally be a giveaway. Buy a book on digital logic and an LA is included! And it does include a dual-channel oscilloscope. Jan Ciger has an alternative to regbits, which I mentioned in the last issue:

|

||||||||

| Freebies and Discounts | ||||||||

This month's giveaway is a Pico 2207B 70 MHz USB scope.

Enter via this link. |

||||||||

| Tidy Benches | ||||||||

In the last issue a reader asked for tips on keeping a lab bench from becoming a mess. Greg Nelson wrote:

Dale Chayes had an interesting story with a picture of his bench. I suspect decluttering guru Marie Kondo would not approve:

Rob Fries has a comment on storing parts:

Mark Peterson wrote:

|

||||||||

| A Risky RISC-V Bet... or Our Future? | ||||||||

RISC-V is an open standard instruction set architecture that is gaining a lot of traction. The Wikipedia entry gives a good overview. In the embedded world I see this as an effort to deal with the Arm tax, where licensees pay Arm a small amount for each processor they sell. For us, this means RISC-V parts could be a bit cheaper than Cortex devices. Yet these are generally already so inexpensive that it would seem to be an issue only in very high-volume applications. Given that RISC-V is an open architecture it's possible to build a customized processor. Add your own instructions or tune others. That could be important in some limited circumstances, though going from an ISA to silicon is not cheap. An FPGA implementation saves foundry costs, though FPGAs will never be a price match for an off-the-shelf MCU. An old argument we hardly ever hear anymore is that the Intel/AMD ISA is a problem since most of the world runs their PCs with these parts, giving a broad attack surface for bad guys. Arm is so ubiquitous that it is an attractive attack target. Diversity is good. The Wikipedia article states that, for the embedded version, "Floating-point instructions should not be supported (the specification forbids it as uneconomical)" which strikes me as rather silly. Cortex M parts are quintessential embedded devices, yet it wasn't long before FPUs became common as floats are the leitmotiv of instrumentation and many other embedded applications. I don't see many embedded systems using RISC-V parts, but these are early days and that could change. IAR and SEGGER both have tool chains; IAR sent me a board with this processor which I haven't had a chance to fiddle with yet. Charles Manning has been thinking about this:

What do you think? |

||||||||

| Design Margins | ||||||||

A recent article in Embedded Computing Design titled "Undervolting for Embedded Systems to Improve Energy-Efficiency" does a real disservice to the EE community. It describes successful efforts to run FPGAs at voltages lower than those specified by the vendors. The probable takeaway, especially for younger engineers not yet seared by the slings and arrows of real world experience, is that one can get some goodies (lower power) by neglecting the datasheet. To be fair, the IEEE article from which this is derived does state "The aim of this paper is to experimentally understand the power and reliability trade-off of commercial FPGAs under aggressive low-voltage operations and its impacts on a FPGA based NN accelerator." Running experiments to increase understanding is admirable. But to take that research and promote it as a possible solution to an engineering problem in a trade magazine strikes me as a disservice to the engineering community. When I went to college we learned that there were equations one used to, for instance, bias a transistor. Run the numbers, and then buy a 2.894k resistor and voila! The circuit will work. The professors never addressed other aspects, like you can't buy that part. Or that the gain of particular transistor's part number can vary by insane amounts. Nor did they talk about design margins, possibly one of the most important aspects of all engineering. What happens if that 3.0V supply is actually 2.9V? Or that 10K resistor is at the end of its tolerance band? Oh, and do the students even learn that a gold band means 5%? My dad, a mechanical engineer, told me that in the 1950s he was working on the F-11F at Grumman. In a test they could not break the tail section. The Navy was upset as the extra strength meant extra weight. When a tail antenna finally snapped the government acquiesced. The tail had, in this case, too much design margin. Would you want to fly on a plane with too little? One of the FPGAs the authors investigated has a Vcc spec of 1.0 V +/- 0.05. The study ran it successfully at two-thirds of that. Interesting? You bet. A good idea? Not for most designs. In my opinion, a fundamental sin in this field is running a part outside of the rated specifications. Yeah, a gamer might immerse a CPU in liquid helium to run it at crazy clock rates, but do that in a real product and you can expect howls of anger from your (former) customers. As a young engineer a mentor drove me mad questioning all of my design decisions. Why did I specify a 1K pullup? Did I consider the gain-bandwidth product of that op amp when the input frequency is near max? What happens to my PID loop if interrupts happen? But he was right, and his incessant badgering made me a better engineer. A friend recently sent me an interesting circuit from a hacker forum. I guess it worked, more or less. Probably some enthusiastic high school kid came up with it. But it was riddled with flaws. On a bench it probably functioned. Make 10,000 copies deployed in the arctic and at the equator, probably not. Hacking is not engineering, whether we're talking about software or hardware design. Engineering is about making something that will work reliably. That includes following the datasheet specifications to the letter, and then adding more margin when possible. For you older folks, perhaps one of the best things you can do as a mentor is to be that nag. Politely, of course, but insistently. |

||||||||

| Failure of the Week | ||||||||

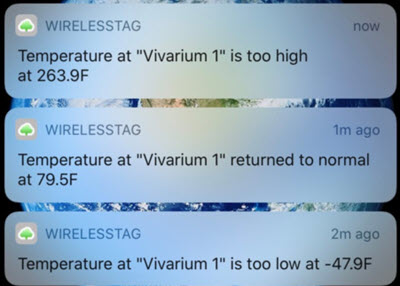

From Nathan Menhorn:

|

||||||||

| This Week's Cool Product | ||||||||

I'm not sure how cool this is, but the big semiconductor vendors are planning to integrate Microsoft's ridiculously-named Pluton chip into their CPUs. From the article: "Microsoft said that the Pluton chip would be integrated as a secure subsystem inside the SoC, adding another layer of protection on top of the internal defenses designed by Intel, AMD, and Qualcomm. The chip establishes a protected area that is physically secluded from the CPU, acting as a vault in charge of protecting secret keys and other information in the PC." Note: This section is about something I personally find cool, interesting or important and want to pass along to readers. It is not influenced by vendors. |

||||||||

| Jobs! | ||||||||

Let me know if you’re hiring embedded engineers. No recruiters please, and I reserve the right to edit ads to fit the format and intent of this newsletter. Please keep it to 100 words. There is no charge for a job ad. |

||||||||

| Joke For The Week | ||||||||

These jokes are archived here. In the last issue the joke section had definitions of various tools. J.G. Harston sent in this alternative one for "hammer": a Birmingham screwdriver:

|

||||||||

| About The Embedded Muse | ||||||||

The Embedded Muse is Jack Ganssle's newsletter. Send complaints, comments, and contributions to me at jack@ganssle.com. The Embedded Muse is supported by The Ganssle Group, whose mission is to help embedded folks get better products to market faster. |