|

|

||||

You may redistribute this newsletter for noncommercial purposes. For commercial use contact jack@ganssle.com. |

||||

| Contents | ||||

| Editor's Notes | ||||

Did you know it IS possible to create accurate schedules? Or that most projects consume 50% of the development time in debug and test, and that it’s not hard to slash that number drastically? Or that we know how to manage the quantitative relationship between complexity and bugs? Learn this and far more at my Better Firmware Faster class, presented at your facility. See https://www.ganssle.com/onsite.htm. |

||||

| Quotes and Thoughts | ||||

While we all know that unmastered complexity is at the root of the misery, we do not know what degree of simplicity can be obtained, nor to what extent the intrinsic complexity of the whole design has to show up in the interfaces. We simply do not know yet the limits of disentanglement. We do not know yet whether intrinsic intricacy can be distinguished from accidental intricacy. - E. W. Dijkstra |

||||

| Tools and Tips | ||||

Please submit clever ideas or thoughts about tools, techniques and resources you love or hate. Here are the tool reviews submitted in the past. |

||||

| The Write-Only Memory's Back Story | ||||

Many are familiar with Signetic's fake Write-Only Memory device, invented back in 1972. A datasheet was produced which gave important specs, like cooling requirements (a six-foot fan one inch away), and graphs showed details like how many pins remained versus number of insertions into a socket. I had a copy of the datasheet (since given away) and posted it on my site. It was a bit messy, and someone gave me .PDFs of a cleaner copy. Turns out, those .PDFs are counterfeit! I can't imagine why anyone would fake a fake datasheet, but John Curtis, the original author of the datasheet, contacted me recently and gave some of the back story. My site once again hosts the original, correct, fake datasheet here. |

||||

| Building Ultra-Low Power Systems | ||||

The Linley Group just released a report (Achieving Energy Efficiency With EFM32 Gecko Microcontrollers) which has an interesting description of the low-power features of Silicon Labs' EFM32 parts. But, it contains the same sort of misinformation - or, at best, hopelessly optimistic claims - that permeates most discussions about this topic. Some MCU vendors are making what I consider outrageous assertions about the ability of their MCUs to run from coin cells for years and even decades. They take a "typical" power consumption number (which in some cases is orders of magnitudes better than worse-case), assume there's no other circuitry involved, and then do a poor analysis of real-world operating conditions. I spent a good chunk of 2013 and 2014 studying the subject and ran numerous experiments to tease out the facts in building systems that have to run for years from a battery. The results were published in a number of articles on embedded.com. Most of what has been written by vendors about this topic turns out to be wrong or naive. There's essentially no way one can build systems that will run reliably for a decade or longer from a coin cell. Even picking the wrong decoupling capacitor will cause the system to fail in a year or two. Most MCU on-board brown-out reset circuits will greatly shorten available battery life. There's a whole host of quite interesting problems and solutions to using coin cells with microcontrollers. The Linley report inspired me to digest those articles into a long article on the subject. Check out Hardware and Firmware Issues in Using Ultra-Low Power MCUs for the real scoop. |

||||

| An Interesting Bug | ||||

It's fun and useful to learn from the experience of others. Bernard Nahas sent in this interesting bug:

|

||||

| Billions and Billions of Transistors | ||||

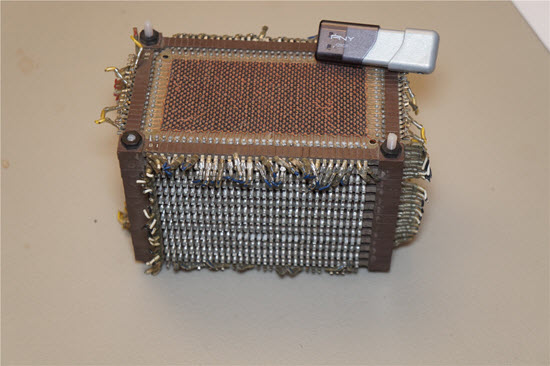

As Paul Simon put it, we live in an age of miracles and wonders, and certainly the electronics industry is the source of plenty of these. I bought a 128 GB flash drive recently. It cost $45. Amazing. Here's a picture of it on top of a core memory array. The core, which I bought from a surplus store in 1971, is 26 planes of 2K bits each for a total of 50K bits. The top plane is visible in this picture and each of those little donuts holds just one bit of data. The flash drive on top holds one trillion bits.

How do they do this? It was impossible to resist the temptation to open the thing up, and these two pictures show the top and bottom of the PCB:

The two big chips, one on top and one on bottom, are SanDisk SDIN5C4-64G devices, which each hold 64 GB of data. The datasheet unsurprisingly notes these are MLC devices, which hold more than one bit per transistor, but doesn't say how many levels each transistor can handle. I suspect it's a 4 level device since SanDisk announced that technology in 2009. That means each chip has over 100 billion transistors. Wow! The bottom picture also shows another chip, which is an NS1081 (from Norelsys) USB controller. The top board has a part labeled "AGHM L422" which I can't find any information about. But that's it for the electronics, other than some capacitors and a 25 MHz oscillator. |

||||

| Jobs! | ||||

Let me know if you’re hiring embedded engineers. No recruiters please, and I reserve the right to edit ads to fit the format and intents of this newsletter. Please keep it to 100 words.

|

||||

| Joke For The Week | ||||

Note: These jokes are archived at www.ganssle.com/jokes.htm. Martin Ostermeyer sent this: A friend of mine once did telephone troubleshooting for his computer-illiterate friend. Problem: the cursor was somehow 'broken'. It took a while to find out that the mouse has to be used 'tail up', not 'tail down'. |

||||

| Advertise With Us | ||||

Advertise in The Embedded Muse! Over 23,000 embedded developers get this twice-monthly publication. . |

||||

| About The Embedded Muse | ||||

The Embedded Muse is Jack Ganssle's newsletter. Send complaints, comments, and contributions to me at jack@ganssle.com. The Embedded Muse is supported by The Ganssle Group, whose mission is to help embedded folks get better products to market faster. |